1. Jurnal[Kembali]

2. Alat dan Bahan[Kembali]

2.1 Hardware

Jumper

Modul D'Lorenzo

a. IC 74LS112 (J-K Flip-Flop)

b. IC 7474 ( D Flip-Flop)

c Switch-SPDT

d. Logic Probe

3. Rangkaian Percobaan[Kembali]

4. Prinsip Kerja[Kembali]

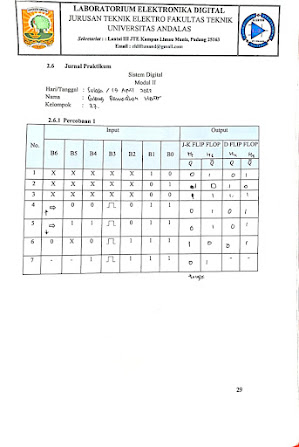

Pada percobaan 1 menggunakan rangkaian D flip-flop dan J-K flip-flop, lalu digunakan juga switch-spdt, logic probe, vcc, dan ground. vcc digunakan menghasilkan tegangan atau memberikan input 1 pada rangkaian dan ground sebagai pemberi input 0.

Pada D flip-flop terdapat inputan B1 dan B0 pada kaki R dan S, lalu B5 pada kaki D, dan B6 pada clk.

Dengan prinsip kerja pada D flip-flop ini yaitu apabila inputan dari kaki R itu berlogika 0 dan S berlogika 1 maka keadaan akan reset(karena diberikan inverter pada kaki R), sedangkan jika kaki S berlogika 0 dan kaki R berlogika 1 maka kedaan akan set(karena diberikan inverter pada kaki S). lalu saat kedua inputan berlogika 0 maka keadan terlarang.

Saat kedua inputan berlogika 0, maka kedaan akan tetap/tanpa perubahan.

Pada J-K flip flop terdapat inputan B1 dan B0 pada kaki R dan S, lalu B2 dan B4 pada kaki J dan K, dan B3 pada clk.

J-K flip flop akan aktif jika R-S nya nonaktifkan, artinya kaki R dan S harus berlogika 1(karena diberikan inverter). Saat clk aktif low maka inputannya 1(karena ada inverter), sedangkan aktif high maka inputannya 0(karena ada inverter).

5. Video[Kembali]

6. Analisa[Kembali]

Analisa Percobaan 1:

1. Bagaimana jika B0 dan B1 sama sama diberi logika 0, apa yang terjadi pada rangkaian?

Pada D flip flop dan J-K flip flop akan terjadi kondisi terlarang, karena kaki R-S diberikan inputan logika 0 sehingga pada rangkaian itu berlogika 1.

2. Bagaimana jika B3 diputuskan/tidak dibubungkan pada rangkaian apa yang terjadi pada rangkaian?

J-K tidak aktif karena clk nonaktif

3. Jelaskan apa yang dimaksud kondisi toggle, kondisi not change, dan kondisi terlarang pada Flip-Flop!

-Kondisi Toggle, terjadi pada JK flip flop dimana saat inputan J dan K berlogika 1. dan outputnya komplemen dari output sebelumya

-Kondisi not change, ketika kedua inputan berlogika 0

-Kondisi terlarang, terjadi pada kaki R dan S memiliki logika 1 sehingga outputnya 1

Tidak ada komentar:

Posting Komentar